Introducing 74HC193 Simulation to LTspice

Monday, April 21st, 2008Ron Fredericks writes: I have completed the design and test of a new component for LTspice/SwitchCAD III circuit simulation and schematic capture. In a previous post I discussed my interest in the 74193 presettable synchronous 4-bit binary up/down counter IC for a digital volume control circuit I am building. The circuit simulation described below focuses on how to simulate the 74HC193 IC, but timing and voltage parameters built into this design allow a designer to easily simulate other variants of this IC from high speed Si-gate CMOS HC and HCT devices to low power Schottky TTL devices.

All circuits related to this 74HC193 simulation are available here>

The 74HC193 Component

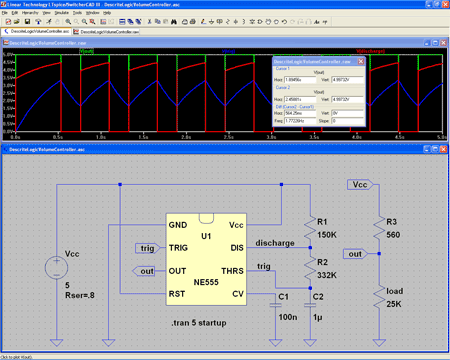

See figure 1 below for a screen shot of the completed design. The circuit was built from the digital gates in the component library supplied with the original Linear Technology’s free LTspice tool.

Figure 1 – 74HC193 Circuit and Related Components

View larger image>

To keep the design looking like the original data sheet logic diagram, as published by companies that include NXP Semiconductors and Texas Instruments, a custom “T notS-R FlipFlop” subcomponent and corresponding assembly file was first created. This subcomponent was reused 4 times in the main IC logic diagram. An assembly file called 74hc193.asy was also created. It includes all pins used on the commercial IC except ground and Vcc. The IC’s internal power supply is not simulated by the Linear Technologies’ gates, and so they are not used or required in this design either.

Each gate within the design has a few variables assigned to them so that the IC remains flexible and easy to reuse in new projects:

- tdgate

td (propagation time delay assigned to each gate)

td (propagation time delay assigned to each gate) - tdgate2

td (propagation time delay assigned to the D FlipFlop)

td (propagation time delay assigned to the D FlipFlop) - tripdtgate

tripdt (td’s accuracy band assigned to each gate including the D FlipFlop)

tripdt (td’s accuracy band assigned to each gate including the D FlipFlop) - vhighgate

logical high value for each gate and D FlipFlop

logical high value for each gate and D FlipFlop - vlowgate

logical low value for each gate and D FlipFlop

logical low value for each gate and D FlipFlop

These variables can be assigned their corresponding time and voltage values using a .param statement placed in the main circuit. These values are then within scope for automatic reuse by the 74HC193 component and flipflop subcomponent simulations. Below is an example of how parameter assignment can be made (as used in the test circuit described next):

.param tdgate=10n tdgate2=3*tdgate tripdtgate=1n vhighgate=5v vlowgate=0v

Technorati Tags: Ron Fredericks, component, LTspice, SwitchCAD III, circuit simulation, schematic capture, 74193, IC, circuit, simulation, timing, voltage, CMOS, Schottky, TTL, Linear Technology

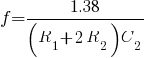

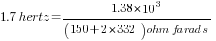

is frequency in hertz

is frequency in hertz is capacitance in farads

is capacitance in farads is resistance in ohms

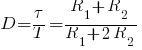

is resistance in ohms is duty cycle

is duty cycle is non-zero output duration

is non-zero output duration is the period of the output

is the period of the output